# User Guide

## CCM-BOOGIE • CompactPCI®

## 3U High Performance Core<sup>™</sup> 2 Duo CPU Board

Document No. 5292 • Edition 19 • 4 May 2012

CCM-BOOGIE

## Contents

| About this Manual                         | 4    |

|-------------------------------------------|------|

| Edition History                           | 4    |

| Related Documents                         | 5    |

| Nomenclature                              | 5    |

| Trade Marks                               | 5    |

| Legal Disclaimer - Liability Exclusion    | 5    |

| Standards                                 |      |

|                                           |      |

| CCM-BOOGIE Features                       | 7    |

| Feature Summary                           | 7    |

| Short Description CCM-BOOGIE              | . 11 |

| Block Diagram CCM-BOOGIE                  |      |

| Top/Bottom View Component Assembly        |      |

| Rear I/O Transition Module CCT-RIO        |      |

| Strapping Headers                         |      |

| Connectors & Sockets                      |      |

| Front Panel Elements                      |      |

| Microprocessor                            |      |

| Thermal Considerations                    |      |

| Main Memory                               |      |

| LAN Subsystem                             |      |

| Serial ATA Interface (SATA)               |      |

| Graphics Subsystem                        |      |

| Real-Time Clock                           |      |

| Universal Serial Bus (USB)                |      |

| LPC Super-I/O Interface                   |      |

| SPI Flash                                 |      |

| Reset                                     |      |

| Watchdog                                  |      |

| PG (Power Good) LED                       |      |

| HD (Hard Disk Activity) LED               |      |

| GP (General Purpose) LED                  |      |

| Hot Swap Detection                        |      |

| Power Supply Status (DEG#, FAL#)          |      |

| PXI Trigger Signals                       |      |

| Mezzanine Side Board Options              |      |

| Rear I/O Options                          |      |

|                                           | 7/   |

| Installing and Replacing Components       | . 48 |

| Before You Begin                          |      |

| Installing the Board                      |      |

| Removing the Board                        |      |

| EMC Recommendations                       |      |

| Installing or Replacing the Memory Module |      |

| Replacement of the Battery                |      |

|                                           | . 52 |

| Technical Reference                       | 52   |

| Local PCI Devices                         |      |

| Local SMB Devices                         |      |

| Hardware Monitor LM87                     |      |

| GPIO Usage                                |      |

|                                           | . 50 |

| GPIO Usage ICH9                          |    |

|------------------------------------------|----|

| GPIO Usage SIO                           |    |

| Configuration Jumpers                    |    |

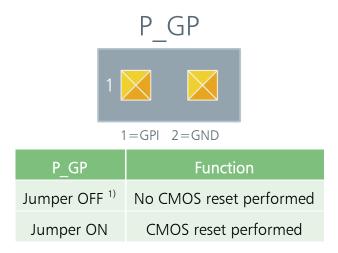

| Reset Jumper BIOS CMOS RAM Values (P_GP) |    |

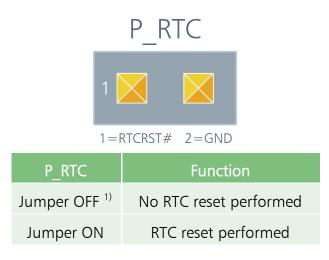

| Reset Jumper ICH9 RTC Core (P_RTC)       | 59 |

| Connectors                               | 60 |

| Front Panel Connectors                   | 60 |

| Video Monitor Connector J_DVI            | 61 |

| Video Monitor Connector J_VGA            | 62 |

| USB Connectors                           |    |

| Ethernet Connectors                      |    |

|                                          | 65 |

| Expansion Interface Header J_EXP         | 65 |

| High Speed Expansion Connector J HSE     |    |

| PCI Express Expansion Header J_PCIE      |    |

| SDVO Expansion Header J SDVO             |    |

| System Reset Header P RST                |    |

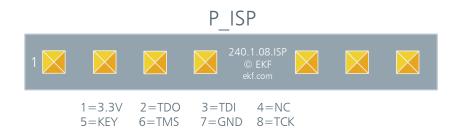

| PLD Programming Header P ISP             |    |

| Processor Debug Header XDP1              |    |

|                                          | 71 |

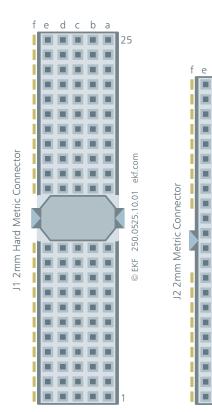

| CompactPCI J2                            |    |

|                                          | 12 |

| Annondix                                 | 71 |

| Appendix                                 |    |

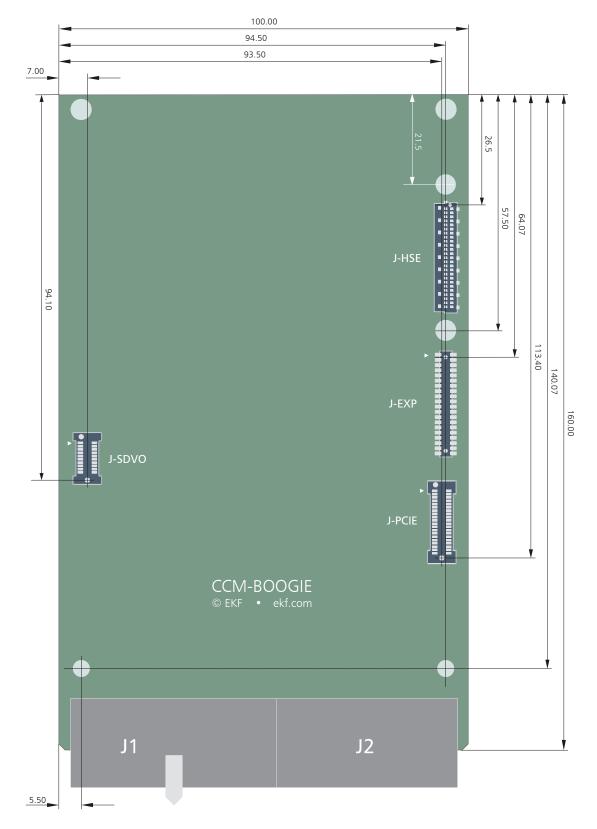

| Mechanical Drawings                      | /4 |

### About this Manual

This manual describes the technical aspects of the CCM-BOOGIE, required for installation and system integration. It is intended for the experienced user only.

## **Edition History**

| Ed. | Contents/Changes                                                                                                                                                                                         | Author | Date              |

|-----|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------|-------------------|

| 1   | User Manual CCM-BOOGIE, english, initial edition (Text #5292, File: ccm_uge.wpd)                                                                                                                         | gn     | 2008-10-27        |

| 2   | Added 'Top View Component Assembly' diagram, changed 'Mechanical<br>Drawings', changed LPC bridge device ID in table 'Local PCI Devices',<br>removed section 'Mass Storage Considerations'.              | gn     | 2008-11-07        |

| 3   | Added chapter 'Mezzanine Side Board Options'                                                                                                                                                             | jj     | 11 November 2008  |

| 4   | Added Images CCM-BOOGIE, Mezzanine Stack                                                                                                                                                                 | jj     | 5 January 2009    |

| 5   | Replaced DVI connector illustration, replaced C44-SATA illustration, table 'Literature' updated and moved to table 'Standards', minor changes throughout text/tables reflecting C42-SATA and CCO-CONCERT | jj     | 19 February 2009  |

| 6   | Corrected SMBus Address of ADT7421.<br>Corrected typo within CompactPCI J2 connection table.<br>Added PCIe-SATA-Bridge JMB362 to local PCI devices table.                                                | gn     | 2009-03-17        |

| 7   | Added power requirements and performance rating for CCM-6 to table<br>'Feature Summary'. Added some images and illustrations of mezzanine<br>modules and side cards.                                     | gn     | 2009-09-01        |

| 8   | Added power requirements for sleep states S3 S4 S5                                                                                                                                                       | jj     | 3 September 2009  |

| 9   | Added photo CCM bottom view                                                                                                                                                                              | jj     | 24 September 2009 |

| 10  | Added photo CCT custom specific version, added photos CCG-CCK-DX1 exploded view, added photo CR4                                                                                                         | jj     | 17 November 2009  |

| 11  | CCH-MARIACHI side card replaced by CCO-CONCERT                                                                                                                                                           | jj     | 19 February 2010  |

| 12  | Added to table Feature Summary: +3.3V V(I/O) option                                                                                                                                                      | jj     | 5 November 2010   |

| 13  | Parallel ATA drives on side cards not supported                                                                                                                                                          | jj     | 1 March 2011      |

| 14  | Added description of unlocked front panel handle signalling                                                                                                                                              | gn     | 2011-04-13        |

| 15  | Added photos showing how to force system shutdown using the front<br>panel handle integrated switch, added photos 'Small Systems' and<br>'Rugged Systems'                                                | jj     | 13 May 2011       |

| 16  | BIOS usage of GP LED - link added                                                                                                                                                                        | jj     | 18 May 2011       |

| 17  | Highlighted BIOS GP LED Usage Link                                                                                                                                                                       | gn     | 2011-06-17        |

| 18  | Added photos of several mezzanine storage modules                                                                                                                                                        | jj     | 23 August 2011    |

| 19  | Added MTBF value to table Feature Summary                                                                                                                                                                | gn     | 2012-05-04        |

#### Related Documents

For ordering information refer to document CCM-BOOGIE Product Information, available at <u>www.ekf.com/c/ccpu/ccm/ccm pie.pdf</u>.

Other documents related to the CCM-BOOGIE - in particular technical information of suitable mezzanine side boards - can be found at <u>www.ekf.com/c/ccpu/ccm/ccm\_e.html</u>.

#### Nomenclature

Signal names used herein with an attached '#' designate active low lines.

#### Trade Marks

Some terms used herein are property of their respective owners, e.g.

- ► **CompactPCI** : ® PICMG

- Windows 2000, Windows XP, Windows Vista: ® Microsoft

- ► EKF, ekf system: ® EKF

EKF does not claim this list to be complete.

#### Legal Disclaimer - Liability Exclusion

This manual has been edited as carefully as possible. We apologize for any potential mistake. Information provided herein is designated exclusively to the proficient user (system integrator, engineer). EKF can accept no responsibility for any damage caused by the use of this manual.

## Standards

| Theme         | Document Title                                                     | Origin                                    |

|---------------|--------------------------------------------------------------------|-------------------------------------------|

| CompactFlash  | CF+ and CompactFlash Specification Revision 3.0                    | www.compactflash.org                      |

| CompactPCI    | CompactPCI Specification, PICMG 2.0 R3.0, Oct. 1, 1999             | www.picmg.org                             |

| DVI           | Digital Visual Interface Rev. 1.0<br>Digital Display Working Group | www.ddwg.org                              |

| Ethernet      | IEEE Std 802.3, 2000 Edition                                       | standards.ieee.org                        |

| HD Audio      | High Definition Audio Specification Rev.1.0                        | www.intel.com/design/chipsets/hdaudio.htm |

| PCI Express   | PCI Express <sup>®</sup> Base Specification 1.1                    | www.pcisig.com                            |

| PCI Local Bus | PCI 2.2/2.3/3.0 Standards PCI SIG                                  | www.pcisig.com                            |

| SATA          | Serial ATA 2.5/2.6 Specification                                   | www.sata-io.org                           |

| TPM           | Trusted Platform Module 1.2                                        | https://www.trustedcomputinggroup.org     |

| USB           | Universal Serial Bus Specification                                 | www.usb.org                               |

#### CCM-BOOGIE Features

#### Feature Summary

| Feature Summary CCM-BOOGIE   |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |  |  |  |  |

|------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|

| Form Factor                  | Single size CompactPCI style Eurocard (160x100mm <sup>2</sup> ), front panel width 4HP (20.3mm)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |  |  |  |  |

| Processor                    | <ul> <li>Designed for Intel® Core<sup>™</sup> 2 Duo SFF (Small Form Factor) processors (codename Penryn), 1066/800MHz FSB, maximum junction temperature 105°C, Enhanced Intel® Speedstep® Technology <sup>1</sup>, Dual Core Multiprocessing <sup>1</sup>, Intel® Virtualization Technology (VT) <sup>1</sup>, Intel® 64 Architecture</li> <li>Core<sup>™</sup> 2 SV • SP9300 • 2.26GHz • FSB 1066MHz • 6MB L2 Cache • 25W TDP Core<sup>™</sup> 2 LV • SL9400 • 1.86GHz • FSB 1066MHz • 6MB L2 Cache • 17W TDP Core<sup>™</sup> 2 ULV • SU9300 • 1.2GHz • FSB 800MHz • 3MB L2 Cache • 10W TDP Celeron® M ULV • 722 • 1.2GHz • FSB 800MHz • 1MB L2 Cache • 5.5W TDP</li> <li><sup>1</sup> features not available with Celeron® M ULV 722 processor</li> </ul>                                                                                                                                                                                                                                                   |  |  |  |  |

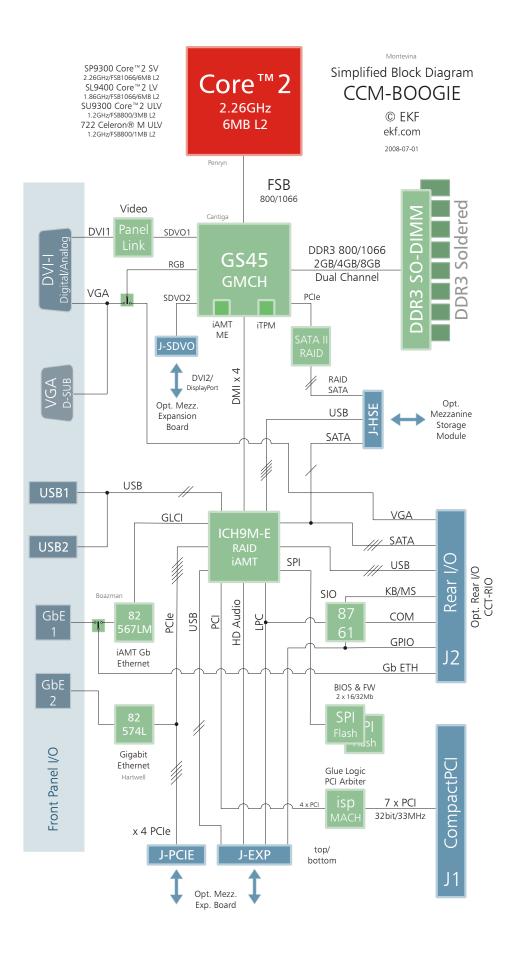

| Chipset                      | <ul> <li>Mobile Intel® 45 (Codename Cantiga) chipset comprised of:</li> <li>GS45 Graphics/Memory Controller Hub (GMCH) with Intel® Gen. 5.0 integrated graphics engine with 10 fully-programmable cores, 1600x1200 dual independent display, HW support for H.264, MPEG2, VC-1, improved 3D capability (DirectX 10/OpenGL 2.0 support), estimated 533-MHz core render clock (low-power mode 266MHz), iAMT manageability engine, option Integrated Trusted Platform Module (ITPM)</li> <li>ICH9M-E Enhanced I/O Controller Hub, integrated GbE MAC, 12 x USB (2 x EHCI, 6 x UHCI cntrls.), 4 x SATA 3Gbps, Intel® Matrix Storage Technology (RAID 0, 1, 5, 10), iAMT, High Definition Audio, unified SPI Flash support</li> </ul>                                                                                                                                                                                                                                                                               |  |  |  |  |

| Memory (RAM)                 | <ul> <li>Maximum memory capacity of 8GB DDR3 up to 1066MHz</li> <li>512Mb, 1Gb, 2Gb, [4Gb] technologies for x8 and x16 devices</li> <li>Channel 0 populated as directly soldered DDR3 devices (Memory Down)</li> <li>Channel 1 provided as 204-pin SODIMM socket to carry DDR3 module PC3-8500</li> <li>Dual channel symmetric – memory addresses interleaved for increased performance (SODIMM module size must match Memory Down size)</li> <li>Intel® Flex Memory Technology (dual channel interleaved mode with unequal memory population) - memory sizes maybe unequal in both the channels</li> <li>Dual channel asymmetric – memory sizes may differ, including no memory module populated in the SODIMM socket (single-channel)</li> </ul>                                                                                                                                                                                                                                                             |  |  |  |  |

| Non Volatile<br>Memory (NVM) | <ul> <li>Intel® Turbo Memory card (codename Robson) on CCI-RAP mezzanine side board optionally available</li> <li>PCI Express Mini Card 1G Byte Flash</li> <li>Microsoft® ReadyDrive and ReadyBoost (Windows® Vista)</li> <li>Intel® Turbo Memory driver</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |  |  |  |  |

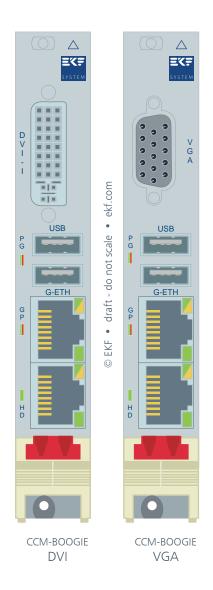

| Video                        | <ul> <li>Both (concurrently) analog monitor and digital flat-panel display support by DVI-I connector (front panel), up to 2048x1536 pixel 16M colours @75Hz refresh rate (analog), up to 1600 x 1200 pixel 16M colours @60Hz (digital), incorporates PanelLink Digital technology (Silicon Image)</li> <li>Dual screen capable 2 x 1600 x 1200 pixel (one display attached to the front panel, the other to the back panel, or both to the front panel by means of a DVI-I to DVI-D/VGA splitter cable, or secondary DVI-D connector on mezzanine side board)</li> <li>Front panel option: D-Sub (female HD15) VGA connector available, replaces DVI-I connector</li> <li>Rear I/O option: Analog video output configurable (BIOS) across J2/P2 CCT-RIO rear I/O transition module</li> <li>Mezzanine option: Secondary DVI-D connector at mezzanine card front panel allows for dual digital flat panel operation, suitable mezzanine modules e.g. CCH-MARIACHI, CCI-RAP, CCJ-RHYTHM, CCO-CONCERT</li> </ul> |  |  |  |  |

|                                | Feature Summary CCM-BOOGIE                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

|--------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| USB                            | <ul> <li>All ports over-current protected, data transfer rate of up to 480Mbps, conforming to USB2.0</li> <li>2 x USB type A connector (front panel)</li> <li>3 x USB ports J2/P2 Rear I/O option (CCT-RIO rear I/O transition module)</li> <li>2 x USB ports via J-EXP expansion interface option (in use by several mezzanine side boards)</li> <li>4 x USB ports via J-HSE (C40-SCFA mezzanine storage module)</li> <li>Dual EHCI / six UHCI controllers provided by ICH9M-E</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

| Ethernet                       | <ul> <li>Two 10/100/1000Mbps Gigabit Ethernet controllers, accessible via RJ45 jacks from the front panel</li> <li>ETH1 equipped with Intel® 82567LM PHY (codename Boazman), serves also as AMT out of band communication path (MAC provided by ICH9M-E), Jumbo Frame support up to 9KB</li> <li>ETH2 equipped with Intel® 82574L GbE controller (codename Hartwell), connected to local PCle lane, supports 9018-byte jumbo packets, TimeSync Offload compliant with 802.1as specification</li> <li>Option ETH1 Gigabit Ethernet configurable (BIOS setup) across J2/P2 with attached CCT-RIO rear I/O transition module</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

| SATA                           | <ul> <li>Total of six 3Gbps SATA channels available</li> <li>Triple-channel Serial ATA 3Gbps available for J2/P2 rear I/O option (derived from ICH9)</li> <li>Suitable rear I/O transition module CCT-RIO (2 x system internal SATA, 1 x eSATA for attachment of external devices)</li> <li>Intel® Matrix Storage Technology MST (Raid 1, 0, Matrix Raid)</li> <li>Secondary on-board PCIe to SATA controller JMB362, dual channel SATA RAID, available via J-HSE expansion connector (plus 1 SATA channel in addition from ICH9)</li> <li>Additional PCIe to SATA controller on mezzanine side boards e.g. CCI-RAP, CCK-MARIMBA, CCL-CAPELLA, CCO-CONCERT</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

| PATA (IDE)                     | <ul> <li>Option mezzanine module attached to J-HSE expansion connector</li> <li>C40-SCFA mezzanine module available with on-board SATA to PATA bridge and<br/>CompactFlash socket</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

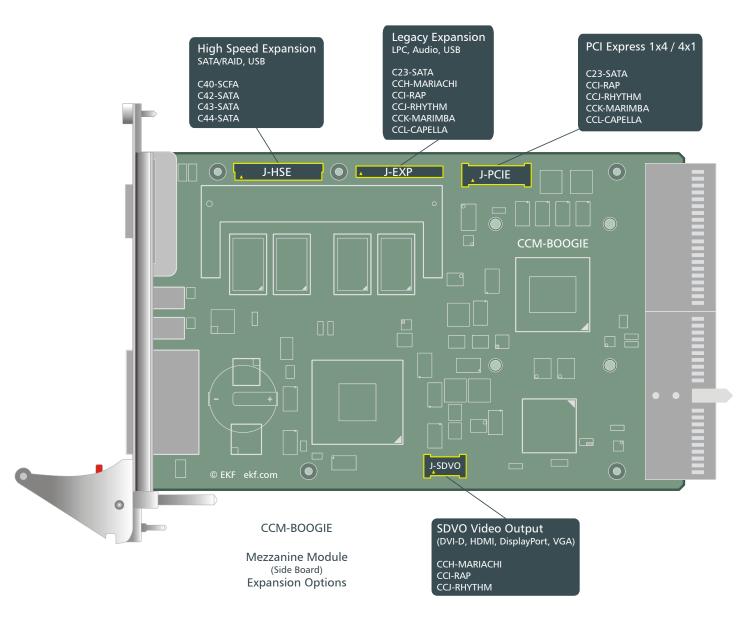

| PCI Express                    | <ul> <li>4-Lane PCIe high-speed connector J-PCIE for CCJ-RHYTHM and other mezzanine expansion cards (side boards)</li> <li>Possible configurations 1 Link x 4 Lanes, 4 Links x 1 Lane</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

| Mezzanine<br>Side Board<br>I/O | <ul> <li>J-EXP Legacy expansion interface connector LPC/USB/Audio (SIO, USB, HD Audio)</li> <li>J-HSE High-speed expansion interface connector (3 x SATA, 4 x USB)</li> <li>J-PCIE PCI Express 4-lane high-speed expansion connector</li> <li>J-SDVO secondary digital graphics port high-speed expansion connector</li> <li>Suitable mezzanine companion side boards available, e.g.:         <ul> <li>CCI-RAP: 2 x PCI Express Mini Card sockets (WLAN, GSM, Wimax, Intel® Turbo Memory), options secondary DVI-D, IEEE 1394 (FireWire), USB SSD, C20-SATA mezzanine storage module (accommodates up to 2 SATA hard disk drives 2.5-inch RAID capable)</li> <li>CCI-RHYTHM: CompactPCI Express system slot controller function by on board 6-port 24-lane PCIe switch, options DVI-D, IEEE 1394 (FireWire)</li> <li>CCL-CAPELLA: Up to 4 Gigabit Ethernet ports, options IEEE 1394 (FireWire), USB SSD, C20-SATA mezzanine module</li> <li>CCO-CONCERT: Audio analog/digital, option secondary DVI-D</li> <li>C23-SATA: PCIe to 2 x SATA 1 x PATA controller</li> <li>C40-SCFA: SATA to PATA bridge &amp; CompactFlash header, option USB SSD, 4HP envelope maintained</li> <li>C41-CFAST: CFast<sup>™</sup> Flash card header, 4HP envelope maintained</li> <li>C42-SATA: 1.8-inch SATA Solid State Drive (SSD), 4HP envelope maintained</li> </ul> </li> </ul> |

|                                                      | Feature Summary CCM-BOOGIE                                                                                                                                                                                                                                                                                                                                                                                                    |

|------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| J2<br>Rear I/O                                       | <ul> <li>Suitable rear I/O transition module CCT-RIO available</li> <li>3 x Serial ATA (SATA), 2 x system internal SATA connectors, 1 x external eSATA connector</li> <li>1 x Gbit Ethernet (switched by BIOS between front panel I/O and rear I/O)</li> <li>3 x USB</li> <li>VGA Analog Video (switched by BIOS between front panel I/O and rear I/O)</li> <li>PS/2 Keyboard, Mouse</li> <li>COM port (TTL Level)</li> </ul> |

| J1<br>CompactPCI®                                    | <ul> <li>ICH9M-E integrated 32-bit PCI bridge, 33MHz 133MBps CPCI master</li> <li>Additional PCI arbiter in PLD for fully figured 8-slot CompactPCI backplane</li> <li>+5V V(I/O) default configuration (PCI pull-up resistors 1k - blue coding key on J1)</li> <li>+3.3V V(I/O) on request (PCI pull-up resistors 2.7k - yellow coding key on J1)</li> </ul>                                                                 |

| CompactPCI®<br>Express                               | <ul> <li>CCM-BOOGIE can be configured as CompactPCI Express System Board (system slot controller) by optionally available mezzanine expansion card (side board) CCJ-RHYTHM</li> <li>CPCIe 4-Link configuration (4-lanes each), for up to 4 CPCIe peripheral slots type 1 and/or type 2 on a passive CPCIe backplane</li> <li>Suitable also for hybrid CPCI/CPCIe systems/backplanes (e.g. Schroff)</li> </ul>                 |

| CompactPCI®<br>Serial                                | <ul> <li>CCM-BOOGIE can be configured as CompactPCI Serial System Board (system slot controller) by optionally available mezzanine expansion card (side board) SJ1-JAM</li> <li>Suitable for hybrid CompactPCI and CompactPCI Serial systems/backplanes</li> </ul>                                                                                                                                                            |

| Platform<br>Management<br>(on Request)               | <ul> <li>Hardware is ready for AMT 4.0 Intel® Active Management Technology (iAMT)</li> <li>ARM core based Manageability Engine (ME) in the GMCH</li> <li>Independent manageability firmware, to be stored in SPI Flash</li> <li>No iAMT BIOS support available as of current</li> </ul>                                                                                                                                       |

| Secure<br>Computing                                  | <ul> <li>Option Trusted Platform Module TPM 1.2 according to Trusted Computing Group specifications</li> <li>Choose from either integrated solution (GS45 Intel® Trusted Execution Technology), or available as discrete controller on several mezzanine boards e.g. CCH/CCI/CCJ</li> <li>Discrete crypto engine silicon brands Infineon or Atmel at users choice</li> </ul>                                                  |

| BIOS                                                 | <ul> <li>Phoenix BIOS with EKF enhancements for embedded systems</li> <li>SPI Flash memory 2 x 16/32/64 Mb</li> <li>Updates available from website ekf.com</li> </ul>                                                                                                                                                                                                                                                         |

| Drivers<br>(All Major OS)                            | <ul> <li>Intel® graphics driver, Intel® embedded graphics driver</li> <li>Intel® networking driver</li> <li>Intel® Matrix Storage Manager software</li> <li>Intel® Turbo Memory driver</li> <li>JMicron SATA driver</li> </ul>                                                                                                                                                                                                |

| Thermal<br>Conditions<br>Environmental<br>Conditions | <ul> <li>Operating temperature: 0°C +70°C (CPU dependent)</li> <li>Storage temperature: -40°C +85°C, max. gradient 5°C/min</li> <li>Humidity 5% 95% RH non condensing</li> <li>Altitude -300m +3000m</li> <li>Shock 15g 0.33ms, 6g 6ms</li> <li>Vibration 1g 5-2000Hz</li> </ul>                                                                                                                                              |

| EC Regulations                                       | <ul> <li>EN55022, EN55024, EN60950-1 (UL60950-1/IEC60950-1)</li> <li>2002/95/EC (RoHS)</li> </ul>                                                                                                                                                                                                                                                                                                                             |

| MTBF                                                 | 141 x 10 <sup>3</sup> h (16 years) @ 50° C                                                                                                                                                                                                                                                                                                                                                                                    |

## User Guide CCM-BOOGIE • High Performance Core<sup>™</sup> 2 Duo 3U *CompactPCI*<sup>®</sup> CPU Board

| Typical Power<br>Requirements                                                                               |              | +3.3V +0                          | .17V/-0.1V                          | +5V +0.25V/-0.15V                 |                                     |  |

|-------------------------------------------------------------------------------------------------------------|--------------|-----------------------------------|-------------------------------------|-----------------------------------|-------------------------------------|--|

| <sup>1)</sup> Intel®<br>SpeedStep®<br>Frequency Modes<br>LFM: Low<br>Frequency Mode,                        | Board        |                                   |                                     |                                   |                                     |  |

|                                                                                                             | board        | MaxPower<br>LFM/HFM <sup>1)</sup> | WinXP Idle<br>LFM/HFM <sup>1)</sup> | MaxPower<br>LFM/HFM <sup>1)</sup> | WinXP Idle<br>LFM/HFM <sup>1)</sup> |  |

| HFM: High<br>Frequency Mode                                                                                 |              | 5.1/5.2A <sup>2)</sup>            | 2.1/2.1A <sup>2)</sup>              | 2.3/4.5A                          | 0.3/0.5A                            |  |

| <sup>2)</sup> Add per Ethernet<br>port 0.4/1.2A (link<br>only/active)<br>@1Gbps or<br>0.1/0.4A @<br>100Mbps | CCM-6-BOOGIE |                                   |                                     |                                   |                                     |  |

|                                                                                                             |              | S4: 1                             | 00mA<br>00mA<br>00mA                | S3: 5<br>S4: 5<br>S5: 3           | 0mA                                 |  |

| Performance<br>Rating                                                                                       | Board        | Processor                         |                                     | CPU/MEM Score                     |                                     |  |

| Measured with                                                                                               | CCM-6-BOOGIE | SP9                               | 300                                 | 5650                              |                                     |  |

| PCMark2005<br>under Windows                                                                                 | CCM-4-BOOGIE | SL9400                            |                                     |                                   |                                     |  |

| XP, 2 x 2GB<br>DDR3 1066                                                                                    | CCM-2-BOOGIE | SU9300                            |                                     |                                   |                                     |  |

Table items are subject to technical changes

#### Short Description CCM-BOOGIE

The CCM-BOOGIE is a versatile 4HP/3U **CompactPCI**<sup>®</sup> CPU board, equipped with an Intel® Core<sup>™</sup> 2 Duo processor at up to 2.26GHz clock, and up to 8GB dual channel capable DDR3 RAM. Four native 3Gbps RAID capable Serial ATA channels are available for mass storage I/O, and in addition another two from a secondary RAID controller. The CCM-BOOGIE has been designed especially for systems which require dual core high performance at moderate power consumption.

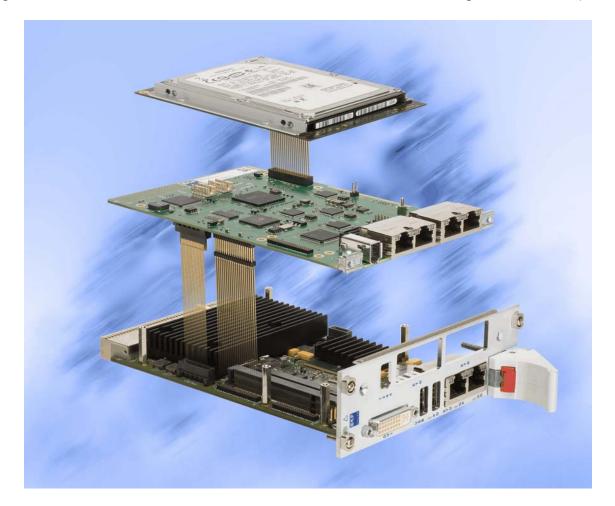

The CCM-BOOGIE is provided with a high performance mobile chipset (Intel® GS45) which operates at up to 1066MHz FSB and up to 1066MHz DDR3 memory clock for optimum system throughput. The chipset is based on PCI Express® technology and has a powerful integrated graphics accelerator. The DVI-I front panel connector enables dual screen video operation. Two Gigabit Ethernet controllers are provided for high speed connectivity (one of them IEEE 802.1as TimeSync compliant). The CCM-BOOGIE is equipped wit a set of local expansion interface connectors, which can be optionally used to directly attach a suitable (application specific) mezzanine side board, e.g. for audio- and legacy support, PCI Express based I/O circuitry, and a secondary DVI video output. Carrier board and side card come as a readily assembled 8HP unit typically. Most mezzanine cards can accommodate in addition a 2.5-inch drive. Also as an option, a suitable rear I/O transition module is available to the CCM-BOOGIE.

As a popular add-on option, the CCM-BOOGIE can be delivered with a small mezzanine module (C42-SATA), which accommodates a 1.8-inch SATA solid state drive (SSD). Alternatively, the C40-SCFA mezzanine card is provided with an industrial grade CompactFlash memory card, and/or an even more rugged USB Silicon State Drive (SSD). Both mezzanine modules fit into the 4HP envelope of the entire assembly.

#### Benefits of the CCM-BOOGIE

- ► High Performance CompactPCI® System Slot Controller with or w/o Rear I/O

- CompactPCI® Express System Board Option (CCJ-RHYTHM Mezzanine Expansion Card)

- Hybrid Systems Option (Dual Backplane CompactPCI® & CompactPCI® Express)

- Intel® Core™ 2 Duo SV (45nm Penryn) Mobile Processor 2.26GHz 6MB L2 Cache (FSB 1066MHz)

- Scalable Series of Small Form Factor (SFF) Processors from 1.2GHz to 2.26GHz

- PCI Express Mobile Intel® 45 Express Chipset GS45 (Cantiga)

- Up to 2 x 4GB DDR3 Memory (Dual Channel Mode Capable, up to 1066MHz)

- One Memory Bank Soldered (Memory Down) for Extreme Ruggedized Systems

- Dual-Screen Graphics Controller

- Dual Gigabit Ethernet Controllers

- Four Native SATA Channels 3Gbps, Intel® Matrix Raid Storage Technology

- Two Additional SATA Channels 3Gbps, RAID capable with JMicron Drivers

- Eleven USB 2.0 channels

- CompactFlash and/or USB SSD with C40-SCFA Mezzanine Module Option (4HP Maintained)

- SATA SSD 1.8-Inch with C42-SATA Mezzanine Module Option (4HP Maintained)

- Variety of Mezzanine Expansion Boards Available with and w/o PCIe

- TPM 1.2 Option (on Mezzanine Expansion Board or GS45 Internally)

- Rear I/O Transition Module Option

- Intel® AMT 4.0 Platform Management

- RoHS compliant

#### Block Diagram CCM-BOOGIE

Top/Bottom View Component Assembly

Bottom View CCM-BOOGIE

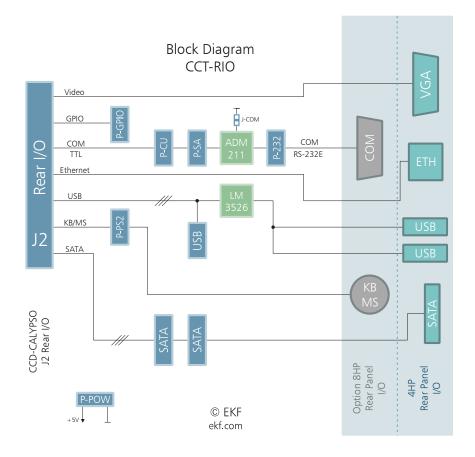

#### Rear I/O Transition Module CCT-RIO

Available as a rear I/O expansion board to the CCM-BOOGIE CPU card, the CCT-RIO is provided with several I/O port connectors, to be used either in addition to the CCM-BOOGIE front panel connectors or alternatively. Being mainly a passive rear I/O transition module, groups of signals from the CCM-BOOGIE CPU board are passed across the CompactPCI J2/P2 connector to the CCT-RIO. Some of the data lines are available locally on the CCT board for system internal wiring only, while other connectors such as VGA-Video and Gigabit Ethernet are mounted into the back panel for external use. USB and SATA (eSATA) channels are provided both on-board and externally.

Typically the CCT-RIO ist equipped with a 4-HP rear panel (20.3mm width). As a custom specific option, an 8-HP panel is available with additional connectors.

Utilization of the CCT-RIO transition module adds a level of I/O functionality that is not available with the CCM-BOOGIE CPU board alone. Further on, swapping the CPU card is simplified by means of rear I/O, which is important for efficient system maintenance (MTTR). Be sure to have ordered a CCM-BOOGIE rear I/O capable version and also the CPCI backplane suitable for rear I/O in order to use the CCT-RIO transition module.

CCT-RIO (Shown with on-Board USB Stick)

User Guide CCM-BOOGIE • High Performance Core<sup>™</sup> 2 Duo 3U *CompactPCI*<sup>®</sup> CPU Board

CCT-RIO Custom Specific Version

## Strapping Headers

| P_ISP | PLD Programming Connector, not stuffed        |

|-------|-----------------------------------------------|

| P_GP  | Jumper to Reset BIOS CMOS RAM Values          |

| P_RST | Jumper to Reset Board                         |

| P_RTC | Jumper to Reset RTC Core of ICH9, not stuffed |

### Connectors & Sockets

| J1/J2                          | CompactPCI Bus 32-bit, 33MHz, PXI, Rear I/O                                                                                                                                                         |

|--------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| J_EXPT<br>J_EXPB <sup>1)</sup> | Expansion Interface Connector (LPC Interface (2 <sup>nd</sup> Super-I/O, 2 <sup>nd</sup> FWH), USB Interfaces, HD Audio Interface, SMBus), available either from top (T) or bottom (B) of the board |

| J_HSE                          | High Speed Expansion Connector (2 x SATA, 4 x USB), Interface to CompactFlash Carrier C40-SCFA                                                                                                      |

| XDP1                           | CPU Debug Port                                                                                                                                                                                      |

| J_PCIE                         | PCI Express Expansion Interface Connector                                                                                                                                                           |

| SODM1                          | 204-pin DDR3 Memory Module SDRAM PC3-8500 Socket                                                                                                                                                    |

<sup>1)</sup> Stuffed on customers request only

#### Front Panel Elements

| Ethernet<br>(GbE1/2) | Dual 1000Base-TX/100Base-TX/10Base-T, RJ-45 Receptacles with integrated indicator LEDs                              |

|----------------------|---------------------------------------------------------------------------------------------------------------------|

| Graphics<br>(DVI-I)  | DVI-I Integrated (digital & analog) Receptacle, suitable for DVI digital flat panel displays and/or analog monitors |

| USB1/2               | Universal Serial Bus 2.0 self powered root hub, type A receptacle                                                   |

| GP                   | General Purpose LED                                                                                                 |

| HD                   | LED indicating any activity on SATA ports                                                                           |

| PG                   | LED indicating Power Good/Board Healthy                                                                             |

#### Microprocessor

The CCM-BOOGIE is designed for use with Core<sup>™</sup>2 Duo processors manufactured in 45nm technology (code name Penryn). These includes also the Ultra Low-Voltage (ULV) and the Low-Voltage (LV) Core<sup>™</sup>2 Duo processors as listed below. The processors are housed in a Small Form Factor (SFF) Micro FC-BGA package for direct soldering to the PCB, i.e. the CPU chip cannot be removed or changed by the user.

The processors supported by the CCM-BOOGIE are running at FSB clock speeds of 800MHz or 1066MHz. The internal Core<sup>™</sup>2 Duo processor speed is achieved by multiplying the host bus frequency by a variable value. The multiplier is chosen by currently required performance and the actual core temperature. To further lowering the power dissipation, the processor is able to halve its FSB clock speed dynamically. This technology is called Enhanced Intel SpeedStep®.

Power is applied across the *CompactPCI* connectors J1 (3.3V, 5V). The processor core voltage is generated by a switched voltage regulator, sourced from the 5V plane. The processor signals its required core voltage by 7 dedicated pins according to Intels IMVP-6 voltage regulator specification.

| 45nm Processors Supported |                    |                           |                      |                     |            |                  |        |          |       |

|---------------------------|--------------------|---------------------------|----------------------|---------------------|------------|------------------|--------|----------|-------|

| Processor                 | Number<br>of Cores | Speed<br>min/max<br>[GHz] | Host<br>Bus<br>[MHz] | L2<br>Cache<br>[MB] | TDP<br>[W] | Die Temp<br>[°C] | CPU ID | Stepping | sSpec |

| ULV Celeron M<br>722      | 1                  | 1.20/1.20                 | 800                  | 1                   | 5.5        | 0-100            | TBD    | TBD      | TBD   |

| ULV Core 2 Duo<br>SU9300  | 2                  | 0.80/1.20                 | 800                  | 3                   | 10         | 0-105            | 10676h | M-0      | SLB5Q |

| LV Core 2 Duo<br>SL9400   | 2                  | 0.80/1.86                 | 1066                 | 6                   | 17         | 0-105            | 10676h | C-0      | SLB66 |

| SV Core 2 Duo<br>SP9300   | 2                  | 0.80/2.26                 | 1066                 | 6                   | 25         | 0-105            | 10676h | C-0      | SLB63 |

#### Thermal Considerations

In order to avoid malfunctioning of the CCM-BOOGIE, take care of appropriate cooling of the processor, GMCH and system, e.g. by a cooling fan suitable to the maximum power consumption of the CPU chip actually in use. Please note, that the processors die temperature is steadily measured by a special controller (ADT7421), attached to the onboard SMBus<sup>®</sup> (System Management Bus). The processor also contains a digital thermal sensor (DTS) that is readable via special CPU registers. DTS allows to get the temperatures of each CPU core separately.

Two further temperature sensors located in the system hardware monitor LM87 allows for acquisition of the boards surface temperature and the thermal state of the onboard system memory channel. Beside this the LM87 also monitors most of the supply voltages. A suitable software to display both, the temperatures as well as the supply voltages, is MBM (Motherboard Monitor), which can be downloaded from the web. After installation, both temperatures and voltages can be observed permanently from the Windows taskbar.

The CCM-BOOGIE is equipped with a passive heatsink. Its height takes into account the 4HP limitation in mounting space of a *CompactPCI* board. In addition, a forced vertical airflow through the system enclosure (e.g. bottom mount fan unit) is strongly recommended (>15m<sup>3</sup>/h or 200LFM around the CPU slot). Be sure to thoroughly discuss your actual cooling needs with EKF. Generally, the faster the CPU speed the higher its power consumption. For higher ambient temperatures, consider increasing the forced airflow to 400 or 600LFM.

The table showing the supported processors above give also the maximum power consumption (TDP = Thermal Design Power) of a particular processor. Fortunately, the power consumption is by far lower when executing typical Windows or Linux tasks. The heat dissipation increases when e.g. rendering software like the Acrobat Distiller is executed.

The Core<sup>™</sup>2 Duo processors support Intel's Enhanced SpeedStep® technology. This enables dynamic switching between multiple core voltages and frequencies depending on core temperature and currently required performance. The processors are able to reduce their core speed and core voltage in multiple steps down to 1200MHz. Furthermore they can reduce their FSB clock speed to half the frequency. This leads to an obvious reduction of power consumption resulting in less heating. This mode of lowering the processor core temperature is called TM2 (TM=Thermal Monitor).

Another way to reduce power consumption is to modulate the processor clock. This mode (TM1) is achieved by actuating the 'Stop Clock' input of the CPU. A throttling of 50% e.g. means a duty cycle of 50% on the stop clock input. However, while saving considerable power consumption, the data throughput of the processor is also reduced. The processor works at full speed until the core temperature reaches a critical value. Then the processor is throttled by 50%. As soon as the high temperature situation disappears the throttling will be disabled and the processors runs at full speed again.

A similar feature is embedded within the Graphics and Memory Controller (GMCH) GS45. An on-die temperature sensor is used to protect the GMCH from exceeding its maximum junction temperature  $(T_{J,max}=100^{\circ}C)$  by reducing the memory bandwidth.

These features are controllable by BIOS menu entries. By default the BIOS of the CCM-BOOGIE enables mode TM2 which is the most efficient.

#### Main Memory

The CCM-BOOGIE features two channels of DDR3 SDRAMs. One channel is realized with 8 memory devices soldered to the board (Memory Down) and delivers a capacity of up to 4GB with a clock frequency of 1066MHz (PC3-8500).

The 2<sup>nd</sup> channel provides a socket for installing a 204-pin SODIMM module thus allowing a simple expansion of system memory (max. module height = 1.25 inch). Supported are unbuffered DDR3 SODIMMs ( $V_{cc}$ =1.5V) without ECC featuring on-die termination (ODT), according the PC3-6400 or PC3-8500 specification. Minimum module size is 256MB; maximum module size is 4GB.

Due to the video requirements of the GS45 chipset, it is recommended to add a SODIMM module with same size as the Memory Down to get best performance (some of the system memory is dedicated to the graphics controller). This typically results in a size of 2x1GB of memory which is recommended to run the operating systems Windows 2000, Windows XP or Windows Vista.

The GS45 chipset supports symmetric and asymmetric memory organization. The maximum memory performance can be obtained by using the symmetric mode. When in this mode, the GMCH accesses the memory channels in an interleaved way. Since the GS45 supports Intels Flex Memory Technology, interleaved operation isn't limited to systems using memory channels of equal capacity. In the case of unequal memory population the smaller memory channel dictates the address space of the interleaved accessible memory region. The remainder of the memory is then accessed in non-interleaved mode.

In asymmetric mode the memory always will be accessed in a non-interleaved manner with the drawback of less bandwidth. The only meaningful application of asymmetric mode is the special case when only one memory channel is populated (i.e. the SODIMM socket may be left empty).

The contents of the SPD EEPROM on the SO-DIMM is used by the BIOS at POST (Power-on Self Test) to get any necessary timing parameters to program the memory controller within the chipset.

#### LAN Subsystem

The Ethernet LAN subsystem is composed of two Gigabit Ethernet ports: One Intel 82567LM Physical Layer Transceiver (PHY) using the ICH9 internal MAC and one Intel 82574L Gigabit Ethernet Controller. These devices provide also legacy 10Base-T and 100Base-TX connectivity. The Ethernet ports are fed to two RJ45 jacks located in the front panel. Each port includes the following features:

- One PCI Express lane per Ethernet port (250MB/s)

- 1000Base-Tx (Gigabit Ethernet), 100Base-TX (Fast Ethernet) and 10Base-T (Classic Ethernet) capability.

- Half- or full-duplex operation.

- IEEE 802.3u, 802.3ab Auto-Negotiation for the fastest available connection.

- Jumperless configuration (complete software-configurable).

- Two bicoloured LEDs integrated into the dedicated RJ-45 connector to signal the LAN link, the LAN connection speed and activity status.

Each device is connected by a single PCI Express lane to the chipset (ICH9). Their MAC addresses (unique hardware number) are stored in dedicated FLASH/EEPROM components. The Intel Ethernet software and drivers for the 82567 and 82574 is available from Intel's World Wide Web site for download.

When managing the board by Intel Active Management Technology (iAMT), the dedicated network port to do so is accessible by the RJ45 connector GbE1.

#### Serial ATA Interface (SATA)

The CCM-BOOGIE provides six serial ATA (SATA) ports each capable of transferring 3Gbps (300MByte/s). Three of the four ports integrated within the ICH9 are routed to the *CompactPCI* J2 connector, thus they are accessible via the rear I/O transition module CCT-RIO. The remainder SATA channel of the ICH9 and two further ports coming from an additional controller (JMicron JMB362) are fed to the high speed expansion connector J\_HSE. This connector allows the installation of local expansion boards like C40-SCFA to attach the popular CompactFlash cards.

A LED named HD located in the front panel, signals disk activity status of the SATA devices.

Available for download from Intel's and JMicron's web sites are drivers for popular operating systems, e.g. Windows® 2000, Windows® XP, Windows® Vista and Linux.

#### Graphics Subsystem

The graphics subsystem is part of the Intel GS45 Graphics/Memory Controller Hub (GMCH). The CCM-BOOGIE offers two digital (SDVO) and one analog (VGA) interface. One of the SDVO ports and the VGA interface is provided by a DVI-I graphics connector. This is both a digital and analog interface. Recent digital input flat-panel displays are widely available with this connector style. For classic monitors, adapters or adapter cables can be used for converting from DVI-I to the 15-pin HD D-SUB connector.

A special display transmitter chip is used to convert Intel's proprietary, PCI express based SDVO interface to the differential DVI signals. The SiI1362 (Silicon Image) transmitter uses PanelLink® Digital technology to support displays ranging from VGA to UXGA resolutions (25 - 165Mpps) in a single link interface.

The 2<sup>nd</sup> SDVO port is fed to the on-board connector J\_SDVO. Expansion boards like CCO-CONCERT feature the display transmitter and provide a 2<sup>nd</sup> DVI channel via a pure digital DVI-D connector. Further more J\_SDVO offers the possibility to gain access to the VESA standard interface called DisplayPort (DP) on future EKF expansion boards.

As an option, the CCM-BOOGIE can be equipped with an ordinary HD D-Sub 15-lead connector (VGA style). This connector is suitable for analog signals only, so the PanelLink transmitter is not stuffed with this option. Nevertheless also flat-panel displays can be attached to the D-Sub connector but with minor reduced image quality.

Independent from the video connector actually in use, DVI or VGA, the VESA DDC 2B standard is supported. This is a two-wire serial bus (clock, data), which is controlled by the GMCH and allows to read out important parameters, e.g. the maximum allowable resolution, from the attached monitor. In addition, DDC Power (+5V) is delivered to either connector. A resettable fuse is stuffed to protect the board from an external short-circuit condition (0.75A).

Graphics drivers for the GS45 can be downloaded from the Intel web site.

#### Real-Time Clock

The CCM-BOOGIE has a time-of-day clock and 100-year calendar, integrated into the ICH9. A battery on the board keeps the clock current when the computer is turned off. The CCM uses a BR2032 lithium battery soldered in the board, giving an autonomy of more than 5 years. Under normal conditions, replacement should be superfluous during lifetime of the board.

#### Universal Serial Bus (USB)

The CCM-BOOGIE is provided with eleven USB ports, all of them are USB 2.0 capable. Two USB interfaces are routed to front panel connectors, two ports are feed to the expansion board interface connectors J\_EXP, four to the high speed expansion connector J\_HSE, and three ports are optionally available for rear I/O across the J2/P2 *CompactPCI* connector.

The front panel USB connectors can source up to 0.5A/5V each, over-current protected by two electronic switches. Protection for the USB ports on the expansion interfaces and on the rear I/O connector is located on expansion boards like CCO-CONCERT-MARIACHI and the CCT-RIO respective. The USB controllers are integrated into the ICH9.

#### LPC Super-I/O Interface

In a modern system, legacy ports as PS/2 keyboard/mouse, COM1/2 and LPT have been replaced by USB and Ethernet connectivity. The 1.4MB floppy disk drive has been swapped against CD- or DVD-RW drives, attached to a SATA connector, or USB memory sticks. Hence, the CCM-BOOGIE is virtually provided with all necessary I/O ports. However, for compatibility purposes the CCM is additionally equipped with a simple Super-I/O chip, for optional rear I/O of PS/2 keyboard/mouse and COM1 (TTL level only) across the J2/P2 CPCI connector. The Super-I/O controller resides on the local LPC bus (LPC = Low Pin Count interface standard), which is a serialized ISA bus replacement.

As an alternative, EKF offers multiple expansion boards to the CCM-BOOGIE, featuring all classic Super-I/O functionality. For example the CCO-CONCERT is a 3U Eurocard with a 4HP (single) width front panel. Access to the connectors PS/2 (mouse, keyboard), COM, USB and audio in/out is given directly from the front panel. The CCO-CONCERT connects to the CCM-BOOGIE across the connectors PEXPT or PEXPB. Usually the CCH is attached to the top of the CCM-BOOGIE. Nevertheless bottom side mounting is possible on customers request.

#### SPI Flash

The BIOS is stored in two flash devices with Serial Peripheral Interface (SPI). 4MByte of BIOS code, AMT firmware and user data may be stored nonvolatile in these SPI flashs (up to 16MByte of flash space is available on request).

The SPI flash contents can be reprogrammed (if suitable) by a DOS or Linux based tool. This program and the latest CCM-BOOGIE BIOS binary are available from the EKF website. Read carefully the enclosed instructions. If the programming procedure fails e.g. caused by a power interruption, the CCM-BOOGIE may no more be operable. In this case you would possibly have to send in the board, because the flash devices are directly soldered to the PCB and cannot be changed by the user.

#### Reset

The CCM-BOOGIE is provided with several supervisor circuits to monitor supply rails like the CPU core voltage, 1.5V, 3.3V or 5V. This circuitry is responsible also to generate a clean power-on reset signal.

Due to lack of space within the front panel the CCM-BOOGIE does not offer a classical push button to force a manual board reset. Nevertheless it is possible to reset the board manually. The ejector within the front panel contains a micro switch that is used to generate a board reset signal. This is done by pushing the red button of the ejector until the handle unlocks without ejecting the board. Immediately after that push up the ejector back to its original position (the red button jumps up as well). Animated GIF: www.ekf.com/c/ccpu/img/reset\_400.gif

The 2<sup>nd</sup> function of the red push button is to act as the board's power button. When pressing besides the reset also a power button event is created.

<u>NOTE:</u> To prevent the board to cause a power button override, the handle should be closed immediately after unlocking the front panel handle. A power button override is triggered by opening the front panel handle for at least 4 seconds. It results in bringing the board to power state S5. In case of entering this state, unlock and lock the front panel handle a 2<sup>nd</sup> time to reenter normal power state S0 again. See also section 'PG (Power Good) LED' to see how the CCM-BOOGIE indicates the different power states.

**WARNING:** The CCM-BOOGIE will enter the power state S5 if the front panel handle is not closed properly when the system powers up. An open handle is signalled by a yellow blinking 'PG LED'.

The manual reset and power button functionality of the front panel handle could be controlled by BIOS Setup.

An alternative (and recommended) way to generate a system reset is to activate the signal PRST# located on CompactPCI connector J2 pin C17. Pulling this signal to GND will have the same effect as to push the handle's red push button.

The healthy state of the CCM-BOOGIE is indicated by the LED PG (Power Good) located in the front panel. This bicoloured LED signals different states of the board (see section below). As soon as this LED begins to shine green all power voltages are within their specifications and the reset signal has been deasserted.

© EKF • ekf.com

#### Watchdog

An important reliability feature is the watchdog function, which is programmable by software. The behaviour of the watchdog is defined within the PLD, which activates/deactivates the watchdog and controls its time-out period. The time-out delay is adjustable in the steps 2, 10, 50 and 255 seconds. After alerting the WD and programming the time-out value, the related software (e.g. application program) must trigger the watchdog periodically. To simplify watchdog programming all watchdog related functions can be done by calling service requests (software SMI's).

The watchdog is in a passive state after a system reset. There is no need to trigger it at boot time. The watchdog is activated on the first trigger request. If the duration between two trigger requests exceeds the programmed period, the watchdog times out and a full system reset will be generated. The watchdog remains in the active state until the next system reset. There is no way to disable it once it has been put on alert, whereas it is possible to reprogram its time-out value at any time.

#### PG (Power Good) LED

The CCM-BOOGIE offers a LED labelled PG located within the front panel. After system reset, this LED defaults to signal different board states:

- Off Sleep state S3, S4 or S5

- Red steady Hardware failure

- Red blink Software failure

- Yellow Management state \$3/M1, \$4/M1 or \$5/M1

- Yellow blink Front panel handle is unlocked <sup>1)</sup>

- Green Healthy

<sup>1)</sup> This feature is available from board revision 1.02.2x forward.

In the states Off or Yellow the LEDs GP and HD decode the kind of sleep state as follows:

| State | Description     | LED GP | LED HD |

|-------|-----------------|--------|--------|

| S3    | Suspend to RAM  | OFF    | ON     |

| S4    | Suspend to Disk | ON     | OFF    |

| S5    | Soft Off        | ON     | ON     |

To enter the PG LED state *Software failure* an appropriate service request by software SMI must be called. The PG LED remains in this red blinking state until the next SMI request is made. After that it falls back to its default function.

#### HD (Hard Disk Activity) LED

The CCM-BOOGIE offers a LED marked as HD placed within the front panel. This LED signals activity on any device attached to the SATA ports. As described above this LED may change its function dependent on the state of the LED PG.

#### GP (General Purpose) LED

Another more programmable bicoloured LED can be observed from the front panel. The status of the red part within the GP LED is controlled by the GPO18 output of the ICH9. Setting this pin to "1" will switch on the red LED. To turn on or off the green LED an appropriate service request (software SMI) must be made.

While the CPU card is controlled by the BIOS firmware, the GP LED is used to signal board status information. A red blinking GP LED is an indication that the BIOS code couldn't start. For details please refer to www.ekf.com/c/ccpu/ccm/firmware/biosinfo.txt.

After successful operating system boot, the GP LED is not dedicated to any particular hardware or firmware function with exception of special states of the LED PG as described above. Hence it may be freely used by customer software.

#### Hot Swap Detection

The *CompactPCI* specification added the signal ENUM# to the PCI bus to allow the board hot swapping. This signal is routed to the GPI3 of the ICH9. A System Management Interrupt (SMI) can be requested if ENUM# changes by insertion or removal of a board.

Note that the CCM-BOOGIE itself is not a hot swap device, because it makes no sense to remove the system controller from a *CompactPCI* system. However, it is capable to recognize the hot swap of peripheral boards and to start software that is doing any necessary system reconfiguration.

#### Power Supply Status (DEG#, FAL#)

Power supply failures may be detected before the system crashes down by monitoring the signals DEG# or FAL#. These active low lines are additions of the *CompactPCI* specification and may be driven by the power supply. DEG# signals the degrading of the supply voltages, FAL# there possible failure. On the CCM-BOOGIE the signal FAL# is routed to the GPI4 and DEG# to the GPI5 of the ICH9.

#### **PXI Trigger Signals**

As an option, the CCM-BOOGIE supports four of the eight trigger signals of the PXI standard, as defined by National Instruments. The trigger signals are provided by the local SIO (Super-I/O) chip IT8761E. GPIO20/21 are routed to TRIG0/1, and GPIO26/27 are used to control TRIG6/7. These signals can also be used as GPIO lines in a non-PXI environment.

#### Mezzanine Side Board Options

The CCM-BOOGIE is provided with several stacking connectors for attachment of a mezzanine expansion module (aka side board), suitable for a variety of readily available mezzanine cards (please refer to www.ekf.com/c/ccpu/mezz\_ovw.pdf for a more comprehensive overview). EKF furthermore offers custom specific development of side boads (please contact sales@ekf.de).

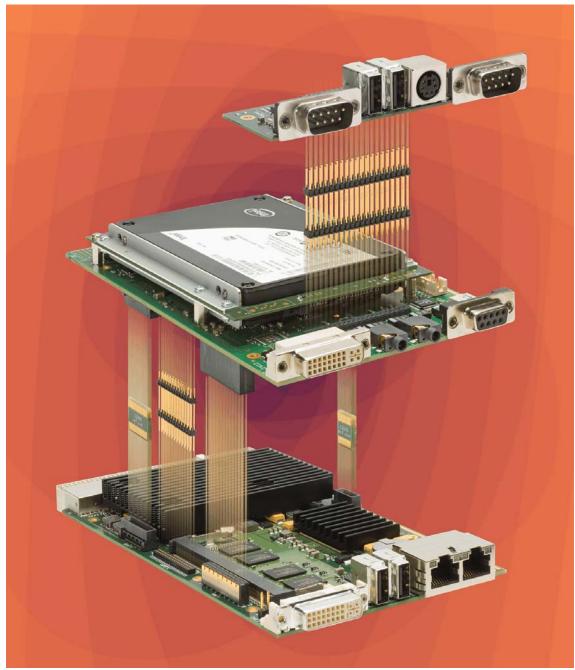

Most mezzanine expansion modules require an assembly height of 8HP in total, together with the CPU carrier board (resulting from two cards at 4HP pitch each).

In addition, cropped mezzanine modules are available for mass storage, which maintain the 4HP envelope (see illustrations next page), for extremely compact systems. Furthermore these small size modules may be combined with the full-size expansion boards (that means an assembly comprised of 3 PCBs).

Due to the SATA/USB mezzanine connector J-HSE, which replaces the P-IDE connector on previous CPU cards, parallel ATA drives on earlier side cards such as the CCJ-RHYTHM are no more supported with the CCM-BOOGIE. Please consider a low profile mezzanine module such as the C41-CFAST (CFast<sup>™</sup> Card), C42-SATA (1.8-inch SATA SSD) or C47-MSATA (mSATA SSD module) as storage solution, mounted between the CCM-BOOGIE and the side card.

## User Guide CCM-BOOGIE • High Performance Core<sup>™</sup> 2 Duo 3U CompactPCI<sup>®</sup> <u>CPU Board</u>

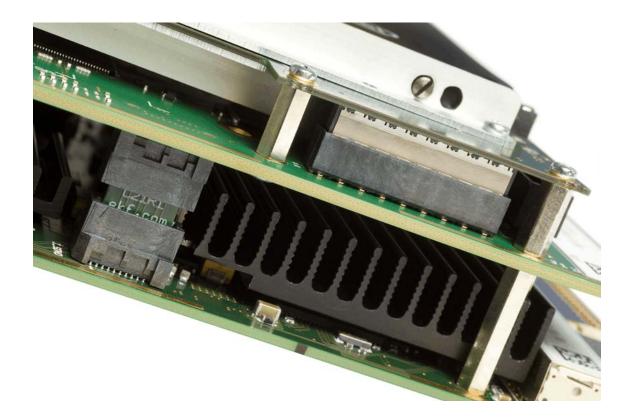

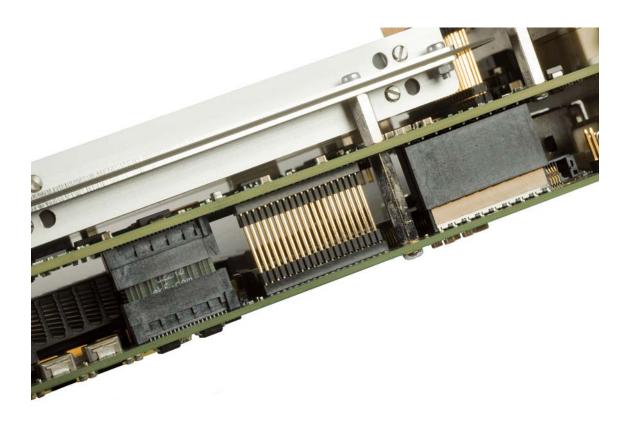

The picture below illustrates a typical mezzanine stack, comprised of the CPU carrier board (shared front panel from 4HP to 12HP, individually tailored to customers configuration), a mezzanine side board with a variety of PCIe and legacy interface functions (front panel and/or rear I/O), and a SATA storage module (either SSD or hard disk, 1.8-inch or 2.5-inch, dual or single drive, RAID option).

CPU Board • PMC/XMC Carrier Side Card • DX1-LYNX XMC Module (Dual Drive)

CCM-BOOGIE with C40-SCFA

C40-SCFA CompactFlash Storage Module

C41-CFAST Storage Module on CPU Carrier Card

C41-CFAST SATA Based Storage Module

CCM-BOOGIE with C42-SATA

C42-SATA Storage Module

CCM-BOOGIE with C43-SATA

C43-SATA I/O Module on CPU Carrier Card

C43-SATA Mezzanine Module

CCM-BOOGIE with C44-SATA

CCM-BOOGIE w. C45-SATA (Internal Drive)

CCM-BOOGIE w. C45-SATA (Removable Drive)

C47-MSATA SSD RAID Storage Module on CPU Carrier Card

C47-MSATA over CPU Carrier Card

CCM-BOOGIE w. C23-SATA Side Board (Picture Similar)

CCM-BOOGIE w. CCO-CONCERT Side Board (Similar Image)

CCM-BOOGIE w. CCI-RAP (Similar Image)

CCM-BOOGIE w. CCJ-RHYTHM Side Board (Picture Similar)

CCM-BOOGIE w. CCK-MARIMBA Side Board

CCM-BOOGIE w. CCL-CAPELLA Side Board (Similar Image)

CCM-BOOGIE w. CCO-CONCERT C20-SATA C32-FIO

CCM-BOOGIE w. CCO-CONCERT C20-SATA C32-FIO

C20-SATA

The C20-SATA is a mezzanine module, available for several side cards to the CCM-BOOGIE. The C20-SATA storage module can be equipped with one or two 2.5-inch drives (SSD or HDD).

C20-SATA Top View

C20-SATA Bottom View (Dual Drive)

| Related Documents Mezzanine Modules and Side Cards                               |                                                            |  |  |  |  |  |

|----------------------------------------------------------------------------------|------------------------------------------------------------|--|--|--|--|--|

| C4x Series www.ekf.com/c/ccpu/c4x_mezz_ovw.pdf<br>Mezzanine Storage Modules      |                                                            |  |  |  |  |  |

| Mezzanine Modules Overview                                                       | Mezzanine Modules Overview www.ekf.com/c/ccpu/mezz_ovw.pdf |  |  |  |  |  |

| The EKF Mezzanine Module Concept www.ekf.com/c/ccpu/cpci_mezzanine_evolution.pdf |                                                            |  |  |  |  |  |

#### Rear I/O Options

Optionally, the CCM-BOOGIE can be used for rear I/O with respect to the following functions:

- Analog Graphics

- 1 Gigabit Ethernet Port

- 3 SATA Ports

- 3 USB Ports

- Keyboard, Mouse

- COM1 (TTL Level)

The pin assignment of the rear I/O connector J2 is chosen to be plugin compatible with EKFs CPU board CCD-CALYPSO and CCG-RUMBA, thus consistent with the rear I/O module CCT-RIO.

The analog graphics and the gigabit ethernet port 1 signals are routed to multiplexers on the CCM-BOOGIE. These switches, controlled by BIOS, select either the front panel or the rear I/O connection. The COM1 port does not include the physical transceiver (TTL level only). This transceiver is located on the rear I/O module CCT-RIO instead.

The CCM is also available in versions suitable for a 64-bit *CompactPCI* backplane. However, the J2/P2 pin assignments of a 64-bit CPCI backplane differ substantially from a *CompactPCI* rear I/O backplane.

To use the rear I/O feature the system in use must be equipped with a P2 *CompactPCI* rear I/O backplane. If the system is provided with a P2 *CompactPCI* 64-bit backplane instead, several of the CCM rear I/O signals will collide with the 64-bit address/data lines on the backplane, with unpredictable results regarding the rear I/O signal integrity.

Single Slot Rear I/O Backplane EKF Part No. 932.4.01.080

Installing and Replacing Components

Before You Begin

### Warnings

The procedures in this chapter assume familiarity with the general terminology associated with industrial electronics and with safety practices and regulatory compliance required for using and

modifying electronic equipment. Disconnect any telecommunication links, networks or procedures described in this chapter. Failure links before you open the system or perform or equipment damage. Some parts of the the power switch is in its off state.

the system from its power source and from modems before performing any of the to disconnect power, or telecommunication any procedures can result in personal injury system can continue to operate even though

## Caution

Electrostatic discharge (ESD) can damage components. Perform the procedures described in this

chapter only at an ESD workstation. If such a some ESD protection by wearing an metal part of the system chassis or board original ESD protected packaging. Retain the

station is not available, you can provide antistatic wrist strap and attaching it to a front panel. Store the board only in its original packaging (antistatic bag and

antistatic box) in case of returning the board to EKF for rapair.

#### Installing the Board

## Warning

This procedure should be done only by qualified technical personnel. Disconnect the system from its power source before doing the procedures described here. Failure to disconnect power, or telecommunication links before you open the system or perform any procedures can result in personal injury or equipment damage.

Typically you will perform the following steps:

- Switch off the system, remove the AC power cord

- Attach your antistatic wrist strap to a metallic part of the system

- Remove the board packaging, be sure to touch the board only at the front panel

- Identify the related *CompactPCI* slot (peripheral slot for I/O boards, system slot for CPU boards, with the system slot typically most right or most left to the backplane)